## Scalus Winter School Storage Systems

Flash Memory

André Brinkmann

## Flash Memory

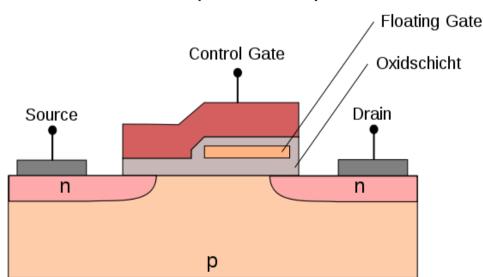

- Floating gate of a flash cell is electrically isolated

- Applying high voltages between source and drain accelerates electrons and improves probability that they float through isolator (in case of positive gate source voltage)

- Fowler-Nordheim tunneling effect

- Bits are persistently stored on the floating gate

- It is only possible to write '0'

- High negative voltage enables information erasure

- Erasure harms isolator

- max. of 1 Mio. erasure cycles

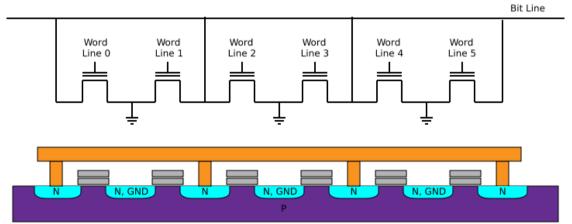

#### NOR-Flash

- Developed as a replacement for EPROMs and ROMs

- Addressing done via standard memory address bus

- No "Glue Logic" between controller and flash

- Can be used to store code

- Bytes can be individually written (Transfer from '1' → '0')

- Only complete blocks can be erased (Reset all bits to '1')

- Block site between64 Kbyte and 256 KByte

- Slow writing data

- Capacity smaller 1 GBit

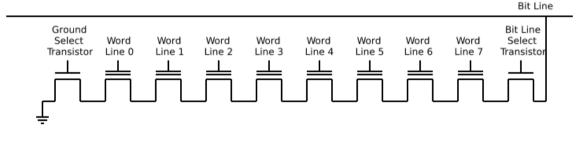

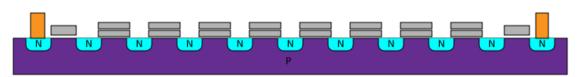

#### NAND-Flash

- NAND flash works page and block oriented

- Page has to be read sequentially and resembles NAND gates

- Page size between 512 Byte and 4 Kbyte

- Additionally 12 to 16 bytes of checksum data

- Pages are combined into blocks

- Pages can only be written once

- without flashing the complete block

- Higher density than for NOR flash

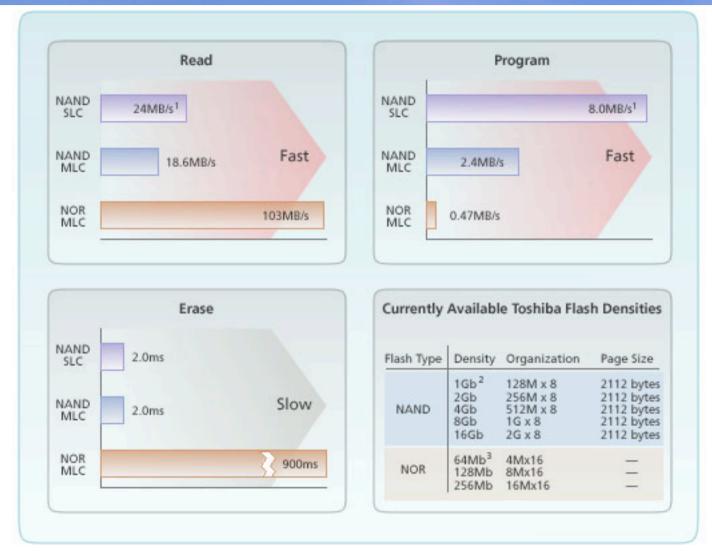

## Comparison NOR/NAND

## Challenges

- Good Performance

- Limited Cost per Unit

- Strong Demands in Reliability

- Access Frequencies

- Tight Coupling with Other Components

- Low Compatibility among Vendors

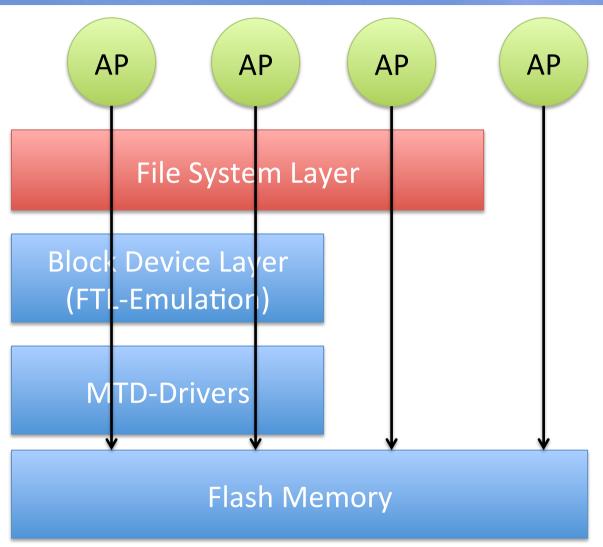

#### Issues – Architecture

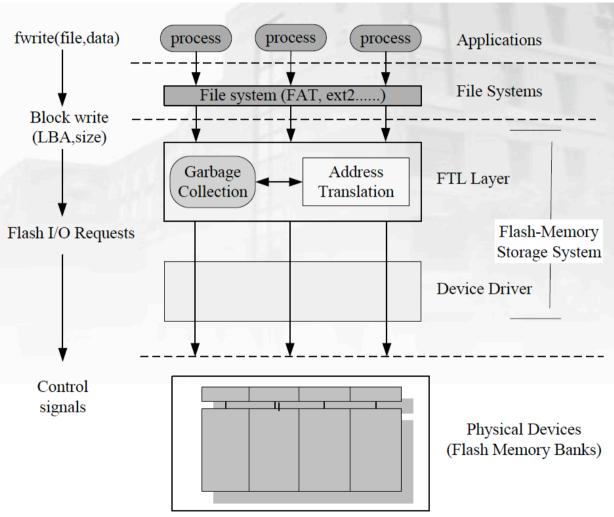

FTL: Flash Translation Layer MTD: Memory Technology Device

#### Write-Once

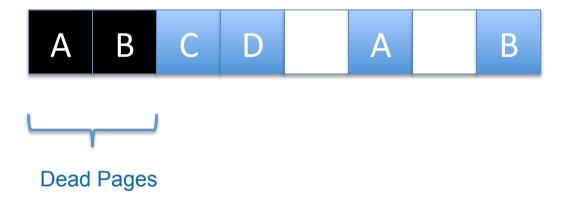

- No writing on the same page unless its residing block is erased

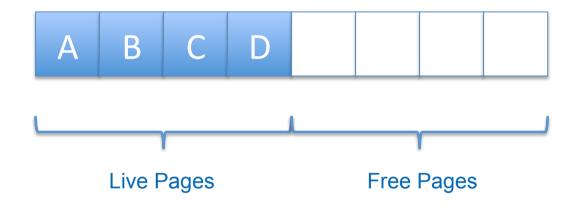

- Pages are classified into valid, invalid, and free pages

#### Bulk-Erasing

Pages are erased in a block unit to recycle used but invalid pages

#### Wear-Leveling

Each block has a limited lifetime in erasing counts

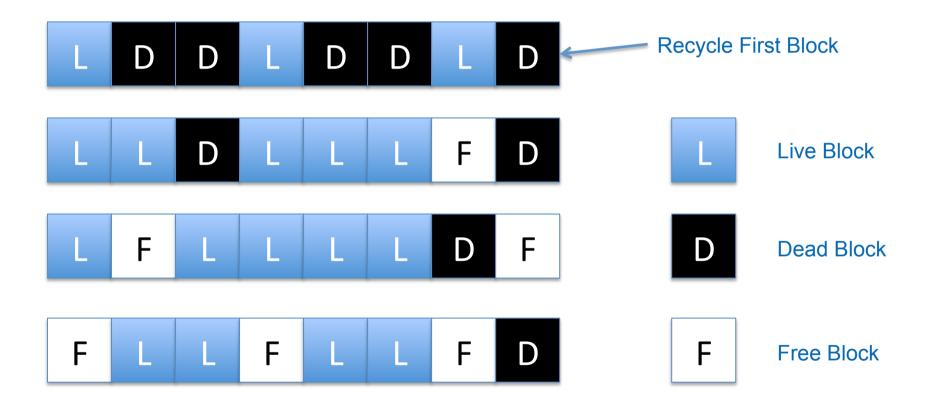

Example: "out-of-place update"

Assume that we want to update pages A and B

Example: "out-of-place update"

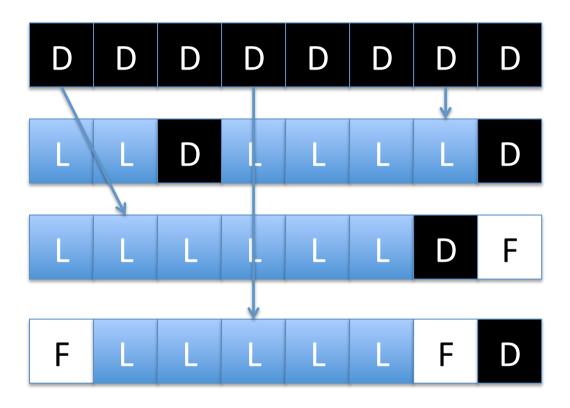

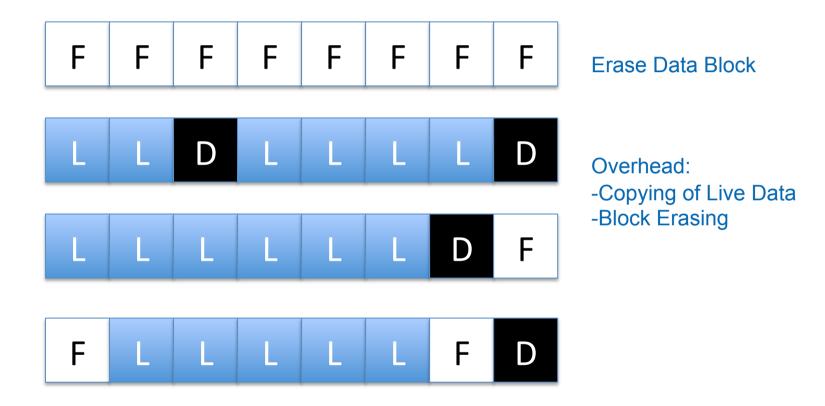

Example 2: Garbage Collection

• Example 2: Garbage Collection

Copy Live Data somewhere else

Example 2: Garbage Collection

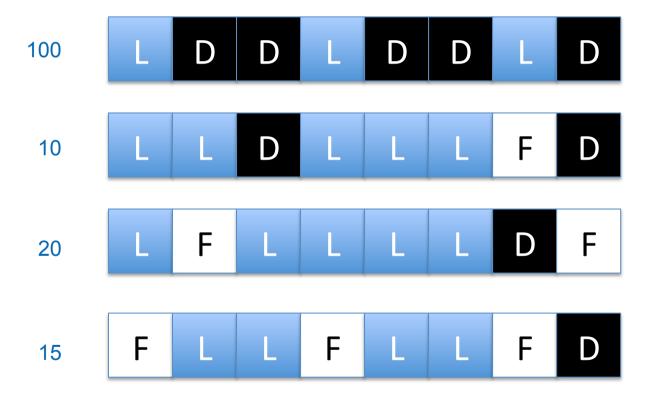

Example 3: Wear-Leveling

**Erase Counter**

#### Hot Data vs. Cold Data

- Hot data usually comes from

- metadata of file-systems

- Small. A piece of hot data is usually  $\leq 2$  sectors.

- structured (or indexed) user files, etc.

- Cold data usually comes from

- read-only (or WORM) files

- E.g., bulk and sequential files that often have a number of sectors

#### Efficient Hot-Data Identification

#### Why Important?

- Wear-Leveling

- Pages that contain hot data could turn into dead pages very quickly

- Blocks with dead pages are usually chosen for erasing

- Hot data should be written to blocks with smaller erase counts

- Erase Efficiency (i.e., effective free pages reclaimed from garbage collection.)

- Mixture of hot data and non-hot data in blocks might deteriorate the efficiency of erase operations

## Flash Translation Layer (FTL)

- A software layer that allows the flash memory to look like a HDD

- Address mapping: logical to physical

- Garbage collection & power-off recovery

- Wear-leveling & bad block management

- Popular FTL algorithms

- FMAX, BAST, FAST, Super block, LAST

- DFTL, DAC, etc...

## Flash Translation Layer (FTL)

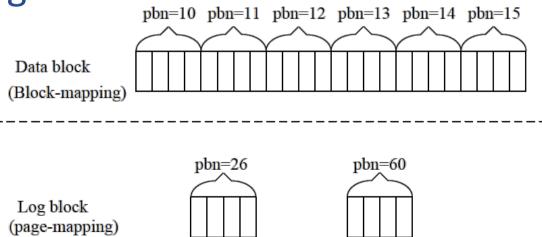

- Page-mapping FTL can map a logical page to any physical page

- Block-mapping FTL can only map a logical page to a fixed offset of a block

- Hybrid FTL includes log blocks

## System Architecture

Embedded Systems and Wireless Networking Lab.

#### Observations

- Write throughput drops significantly after garbage collection starts

- The capacity of flash-memory storage systems increases very quickly such that also memory space requirements for address translation growth quickly

- Reliability becomes more and more critical when the manufacturing capacity increases

- Significant increment of flash-memory access numbers

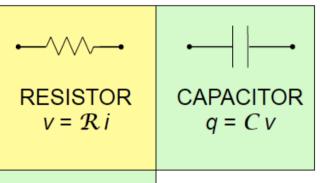

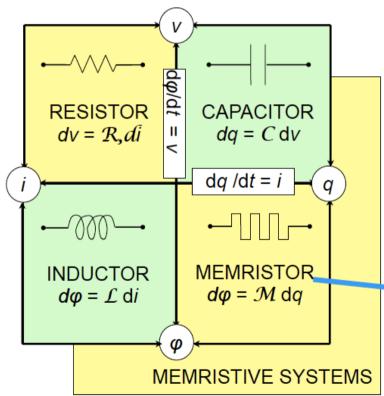

## 3 passive linear circuit elements

Resistor – 1827 Georg Ohm

INDUCTOR  $\varphi = \mathcal{L} i$

Capacitor - 1745 Volta / von Kleist & van Musschenbroek Benjamin Franklin

Inductor – 1831 Michael Faraday Joseph Henry

# Chua generalizes circuit theory to nonlinear systems

- L. O. Chua, "Memristor the missing circuit element," IEEE Trans. Circuit Theory 18, 507–519 (1971)

- L. O. Chua and S. M. Kang, "Memristive devices and systems," *Proc. IEEE, 64 (2), 209-23 (1976)*

- Memristor "remembers" changes in the curren its resistance

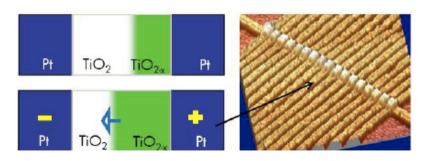

- D. Strukov, G. Snider, D. Stewart & S. Williams: The missing memristor found. In: Nature. 453, 2008, S. 80-83

#### Memristors

#### Advantages

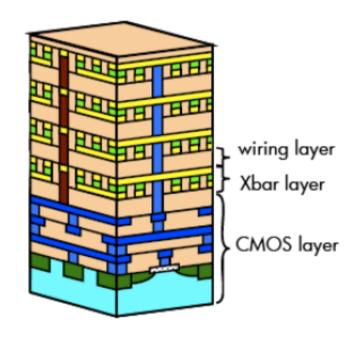

- Fast, cheap, dense, & low energy

- Can be fabbed with CMOS logic &3D layers on single die

#### Challenges

- Understand wear out

- Moving from the lab to the fab

## Phase-change memory (PRAM)

- PRAM based on unique behavior of chalcogenide glass

- Each memory cell contains a material that has two phases with very different electrical properties

- An "amorphous phase" exhibits high resistivity, while a "crystalline phase" has much lower resistivity

- Reading the bit value stored in a cell consists of sensing its resistivity (a fast, low-power operation)

#### PRAM

- Individual PRAM cells can be programmed independently of other cells

- When overwriting data stored in PRAM, only cells whose current value differs from the new value to be written need to be updated

- Degrades much more slowly than Flash

- Challenges:

- requirement of high programming current density

- long-term resistance and threshold voltage drift

#### **PRAM**

- In order to change the bit value stored in a PRAM cell, the phase-change material must be brought into a different phase by heating

- Heating the phase-change material to its crystallization temperature for a sufficiently long period of time causes it to get into its crystalline state

- Heating it to a yet higher temperature for a short period of time makes the material amorphous

- Both of these operations require high-power current pulses (relative to the read operation)